Узел ИЧ

6. УСТРОЙСТВО И РАБОТА СОСТАВНЫХ ЧАСТЕЙ ИЗДЕЛИЯ

6.1. Узел ИЧ.

6.1.1. Узел измерения частоты ИЧ предназначен для фильтрации и преобразования уровня входного измеряемого сигнала; измерения его периода; сравнения результатов измерения с заданными уставками по частоте; формирования шести выходных сигналов, отражающих результаты сравнения входной частоты с уставками; генерации тактовых частот и для формирования сигнала блокировки.

6.2.1. Входные сигналы узла ИЧ:

- напряжение измеряемого сигнала от входной цепи;

- напряжения питания +12 В, минус 12 В, +5 В.

Выходные сигналы узла ИЧ:

- ЧАПВ-A - логическая единица, если частота измеряемого сигнала больше уставки FЧАПВ-A;

- ЧАПВ-B - логическая единица, если частота измеряемого сигнала больше уставки FЧАПВ-B;

- D - логический ноль, если частота измеряемого сигнала меньше или равна уставке FD; логическая единица, если частота измеряемого сигнала больше уставки FD

- АЧР-A - логический ноль, если частота измеряемого сигнала меньше или равна уставке FАЧР-A;

- АЧР-B - логический ноль, если частота измеряемого сигнала меньше или равна уставке FАЧР-B;

- АЧР-C - логический ноль, если частота измеряемого сигнала меньше или равна уставке FАЧР-C;

- 7 ТАКТ - импульс логического нуля;

- БЛОК - логическая единица при наличии сигнала блокировки;

- 10 ms - тактовый сигнал с периодом 10 мс;

- ВЫХОД ЗАПРЕТА - уровень минус 12 В, если частота входного сигнала больше заданной уставки; высокое сопротивление, если частота входного сигнала меньше или равна уставке.

6.2.2. В состав узла ИЧ входят: логарифмирующий усилитель; фильтр низких частот; фильтр высоких частот; компаратор сигнала; схема блокировки; формирователь сбросов; счётчик интервала; счётчик периода; распределитель; коммутатор уставок; устройство сравнения; задающий генератор; делитель частоты; формирователь сигнала запрета; логический тестер.

Логарифмирующий усилитель предназначен для сжатия динамического диапазона входного сигнала (совместно со входной цепью) и усиления его до уровня, оптимального для работы фильтров. Логарифмирующая цепь состоит из диодов V1 - V6 и резисторов R1, R2. Конденсатор C1 служит для уменьшения уровня высокочастотных помех на входе усилителя D4.1, коэффициент усиления которого задаётся резисторами R3, R5 и равен двум.

Фильтр низких частот состоит из звена второго порядка R8, R15, C14 - C16, заграждающего звена R17, R18, C17 - C20, усилителя D4.2 и предназначен для устранения влияния на работу узла гармоник измеряемого сигнала и высокочастотных помех. Частота среза (54 - 62) Гц подбирается резистором R20*.

Фильтр высоких частот состоит из звена второго порядка C22, C23, R35, R36, R38, заграждающего звена C24, C25, R38, R42, R43, звена первого порядка C26, R45, R48, усилителей D14.1, D14.2 и предназначен для уменьшения влияния на работу узла низкочастотных помех. Частота среза (39 - 45) Гц подбирается резистором R38*.

Компаратор сигнала состоит из интегрирующей цепи R49, C27, усилителя-ограничителя D12.2, R50, R51, триггера Шмитта D20.2 и предназначен для преобразования измеряемого сигнала в импульсы уровня КМОП. С помощью соединителя X9 можно подать на вход триггера сигнал с внешнего испытательного устройства.

Схема блокировки предназначена для контроля уровня измеряемого сигнала, формирования сигнала блокировки при его уменьшении ниже установленного порога и при снижении напряжения питания 12 В и для формирования задержки снятия блокировки при восстановлении нормальных уровней сигнала.

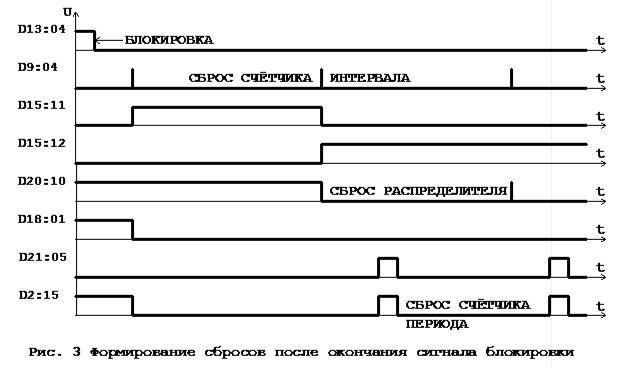

Сигнал с выхода D4.1 поступает на инвертирующий усилитель D5.1, R6, R7 и на диод V8, который совместно с V9 и R10 образуют двухполупериодный выпрямитель, выход которого подключен ко входу 2 компаратора D5.2. Если сигнал на входе 2 больше напряжения, формируемого цепью R12, V10, R13*, которая определяет порог блокировки, на выходе микросхемы D5.2 присутствуют положительные импульсы, которые через делитель R11, R14 сбрасывают счётчик D7.2, в результате чего на его выходе 06 постоянно имеется логический ноль. На вход 2 микросхемы D7.2 поступают тактовые импульсы с периодом 1024 мкс с делителя частоты. Если в течение 8 мс на вход 7 микросхемы D7.2 не поступит импульс сброса, на выходе 06 микросхемы D7.2 появляется логическая единица, которая блокирует счётчик D7.2 и через диод V14 сбрасывает счётчик задержки D11. На выходе 05 микросхемы D11 формируется сигнал блокировки, который через инвертор D13.1 поступает на схемы узла ИЧ, через инвертор D13.2 зажигает индикатор H1 “НЕТ U ИЗМ” и через инвертор D13.4 поступает на выход узла. С выхода 08 микросхемы D14.1 через диод V17 сигнал поступает на цепь C21, R21 и на вход 05 компаратора D12.1. Пока напряжение на C21 выше напряжения на R13*, на выходе 06 микросхемы D12.1 напряжение отрицательное и диод V18 закрыт. При снижении напряжения на C21 на выходе 06 микросхемы D12.1 появляется импульсное или постоянное положительное напряжение, которое через цепь R37, V18 сбрасывает счётчик задержки D11. Пока напряжение в цепи +12 В превышает 10 В, на выходе элемента D20.1 логический ноль и диод V16 закрыт. При снижении напряжения на выходе элемента D20.1 появляется логическая единица, которая через диод V16 поступает на вход сброса счётчика задержки D11. При отсутствии импульсов сброса счётчик D11 заполняется импульсами с периодом 10 мс, поступающими на вход 10 микросхемы D11.1. Через 640 мс на выходе 05 микросхемы D11 появляется логическая единица, счётчик самоблокируется и сигнал блокировки снимается со схем узла ИЧ. С приходом первого после снятия блокировки импульса входной частоты на выходе 11 счётчика D15.2 появляется уровень логической единицы, который сбрасывает триггер блокировки счётчика периода D18.1. С приходом последующих импульсов входной частоты на входе 9 элемента D20.1 появляется логическая единица и снимается блокировка распределителя. С приходом восьмого импульса входной частоты на выходе 14 элемента D15.2 появляется логическая единица, счётчик D15.2 самоблокируется и снимается сигнал блокировки с выхода элемента D13.4.Формирователь сбросов предназначен для формирования импульсов сброса счётчика интервала, распределителя и счётчика периода.

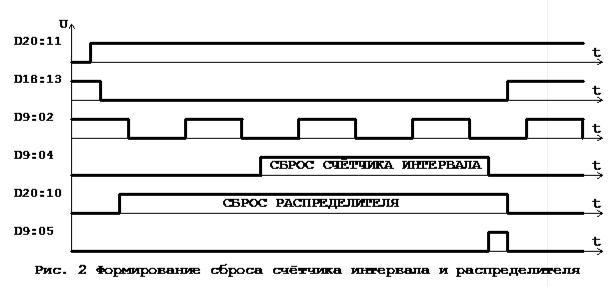

Схема на элементах D9.2 и D18.2 формирует по каждому положительному

При поступлении импульса сброса счётчика интервала на выходе 05 счётчика интервала и импульс длительностью (3 - 4) мкс для сброса распределителя. На элементах D15.2, D18.1, D20.3 выполнена схема последовательного снятия сбросов после окончания сигнала блокировки. Временные диаграммы работы формирователя сбросов изображены на рис. 2, 3.

Счётчик интервала выполнен на элементах D2.2, D6.2, D8.2, D15.1 и предназначен для формирования калиброванного интервала 16.386 мс, тактовых импульсов с частотой 500 кГц для работы счётчика периода и тактовых импульсов с периодом 1.024 мс для работы распределителя.

Через 16.386 мс на выходе 05 микросхемы D8.2 появляется логическая единица и разрешается работа счётчика периода.

Счётчик периода выполнен на элементах D2.1, D6.1, D8.1, D10 и предназначен для отсчёта разницы между периодом измеряемого сигнала и длительностью калиброванного интервала 16.386 мс.

При появлении логической единицы на выходе 05 микросхемы D8.2 на выходе 01 микросхемы D10.1 появляется логический ноль и счётчик периода начинает считать импульсы с частотой 500 кГц, поступающие на вход 10 микросхемы D2.1. Если время счёта превышает 7.68 мс, на выходе 13 микросхемы D10.1 появляется логический ноль, на выходе 01 микросхемы D10.2 логическая единица и работа счётчика периода блокируется. Соответствующая этому случаю частота составляет 41.56 Гц.

Между окончанием импульса разрешения и началом импульса сброса в счётчике периода хранится результат измерения длительности предыдущего периода.

Распределитель выполнен на микросхеме D21 и предназначен для формирования импульсов управления коммутатором уставок, записи в выходной формирователь результатов сравнения измерянного периода и уставок, сброса счётчика периода и самоблокировки.

Состояния распределителя после окончания импульса сброса приведены в табл. 1.

Таблица 1

Номер такта |

Логич. единица на выходе D21: | Длитель-ность, мс | По импульсу, сравнение с уставкой: | По фронту, запись результата сравнения с уставкой: |

| 0 | 03 | 0.512 | FАЧР-C | |

| 1 | 02 | 1.024 | FD | FАЧР-C |

| 2 | 04 | 1.024 | FЧАПВ-B | FD |

| 3 | 07 | 1.024 | FЧАПВ-A | FЧАПВ-B |

| 4 | 10 | 1.024 | FАЧР-B | FЧАПВ-A |

| 5 | 01 | 1.024 | FАЧР-A | FАЧР-B |

| 6 | 05 | 1.024 | Сброс счётчика периода | FАЧР-A |

| 7 | 06 | - | Самоблокировка |

Коммутатор уставок выполнен на буферных инверторах D22, нагрузочных резисторах R23, R24, соединителях X3 - X8, диодах V19 - V78, V80 - V91 и предназначен для поочерёдной подачи на входы устройства сравнения шести двенадцатиразрядных двоичных чисел.

Импульсы логической единицы с выходов распределителя D21 поочерёдно вызывают появление логического нуля на выходах инверторов D22; группы диодов, определяемые установленными на соединителях X3 - X8 перемычками, открываются и на выходе коммутатора уставок появляется двенадцатиразрядное двоичное число, соответствующее заданной уставке по частоте.

С помощью соединителей X3 - X8 выставляются уставки:

- соединитель X3 - уставка FАЧР-A;

- соединитель X4 - уставка FАЧР-B;

- соединитель X5 - уставка FЧАПВ-A;

- соединитель X6 - уставка FЧАПВ-B;

- соединитель X7 - уставка FD;

- соединитель X8 - уставка FАЧР-C.

Частота уставки определяется по формуле:

F = 500000 / (8193 + К),

где К - двенадцатиразрядное двоичное число, устанавливаемое перемычками на соединителях X3 - X8 (см. табл. 1 приложения);

К = (XiC × 2048) + (XiB × 1024) + (XiA × 512) + (Xi9 × 256) + (Xi8 × 128) + (Xi7 × 64) + (Xi6 × 32) + (Xi5 × 16) + (Xi4 × 8) + (Xi3 × 4) + (Xi2 × 2) + (Xi1 × 1),

где XiJ - J-ый разряд на соединителе Xi; при снятой перемычке XiJ =1; при установленной перемычке XiJ = 0.

Пример 1: на соединителе X3 сняты перемычки 3, 5, 6, 8, C; остальные перемычки установлены. Находим К:

К = (1 × 2048) + (0 × 1024) + (0 × 512) + (0 × 256) + (1 × 128) + (0 × 64) + (1 × 32) + (1 × 16) + (0 × 8) + (1 × 4) + (0 × 2) + (0 × 1) = 2228;

FАЧР-A = 500000 / (8193 + 2228) = 47.98004 Гц.

Пример 2: необходимо установить частоту АЧР-B равной 49.20 Гц.

Находим К = (500000 / 49.20) - 8193 = 1969,6; округляем до ближайшего целого числа К @ 1970; находим коэффициенты XiJ:

1970 = (0 × 2048) + (1 × 1024) + (1 × 512) + (1 × 256) + (1 × 128) + (0 × 64) + (1 × 32) + (1 × 16) + (0 × 8) + (0 × 4) + (1 × 2) + (0 × 1);

делаем вывод: на соединителе X4 необходимо снять перемычки в разрядах B, A, 9, 8, 6, 5, 2, остальные перемычки соединителя X4 должны быть установлены.

Устройство сравнения выполнено на микросхемах D16, D17, D19 и предназначено для сравнения числа, хранящегося в счётчике периода, с числом, поступающим с коммутатора уставок.

Если число в счётчике периода больше или равно числу с коммутатора уставок (то есть частота измеряемого сигнала меньше или равна частоте уставки), на выходе 13 микросхемы D19 формируется логический ноль; если частота измеряемого сигнала больше частоты уставки, на выходе 13 микросхемы D19 формируется логическая единица.

Выходной формирователь выполнен на микросхемах D23 - D27 и предназначен для хранения результатов сравнения измерянной входной частоты и уставок и усреднения результатов сравнения за три периода измеряемого сигнала. Выходной формирователь состоит из шести одинаковых устройств, каждое из которых представляет собой сдвигающий регистр и мажоритарный элемент, входы которого подключены к выходам первых трёх разрядов регистра. На информационные входы регистров поступает сигнал с выхода устройства сравнения, а на входы записи - импульсы с соответствующих выходов распределителя. Для правильной работы устройства D в режиме реле скорости снижения частоты регистр D24.1 сбрасывается в состояние, при котором на всех его выходах присутствуют логические нули, при поступлении сигнала блокировки.

Задающий генератор частоты 1 МГц выполнен на микросхеме D3 по схеме несимметричного мультивибратора с кварцевым резонатором Z1 цепи положительной обратной связи. С помощью конденсатора C2 осуществляется точная настройка частоты.

Делитель частоты выполнен на двоичных счётчиках D1.1, D1.2, D7.1, D9.1. С помощью элементов V7, V11 - V13, R16 общий коэффициент деления установлен равным 10000. Таким образом на выходе делителя формируется сигнал с периодом 10 мс, который через буферный элемент D13.5 поступает на выход узла.

Формирователь сигнала запрета выполнен на элементах V92, V93, C28, R53 - R56, X10 и предназначен для выдачи сигнала “ВЫХОД ЗАПРЕТА” на однотипное изделие при организации двухвходовых схем. С помощью соединителя X10 эмиттер транзистора V92 подключается к выходу одного из формирователей FD, FАЧР-A, FАЧР-B или FАЧР-C. Если на выходе выбранного формирователя логический ноль, транзисторы V92, V93 закрыты и выход схемы находится в высокоомном состоянии. При появлении на выходе выбранного формирователя логической единицы транзисторы открываются и на контактах А7, Б7 соединителя X1 узла ИЧ (и на контакте X4:2 аппаратуры АЧРМ) появляется напряжение минус 12 В.

Логический тестер выполнен на элементе D13.3, резисторах R39, R40, R47, индикаторе H2 “ТЕСТ” и предназначен для индикации логического уровня входного сигнала тестера (вход тестера выведен на контакт 1 соединителя X2 узла ИЧ, расположенного на лицевой панели узла ИЧ). При отключенном входе тестера или при подаче на его вход логического нуля индикатор H2 не светит, при подаче на вход тестера логической единицы индикатор “ТЕСТ” светится.

Никто пока не комментировал эту страницу.